IN Brief:

- Chiplet packages are hitting power and latency limits with electrical fabrics.

- CEA’s prototype adds frame-level optical path setup and wavelength-flexible links.

- The work points to optical networking behaving more like an on-package switch.

Researchers from CEA-List and CEA-Leti have presented an electro-optical router at ISSCC 2026 that targets a stubborn constraint in silicon photonics for advanced packaging: most optical interconnects inside packages still behave like static point-to-point links, with configuration and training latencies that are acceptable at board scale, but awkward inside dense chiplet systems.

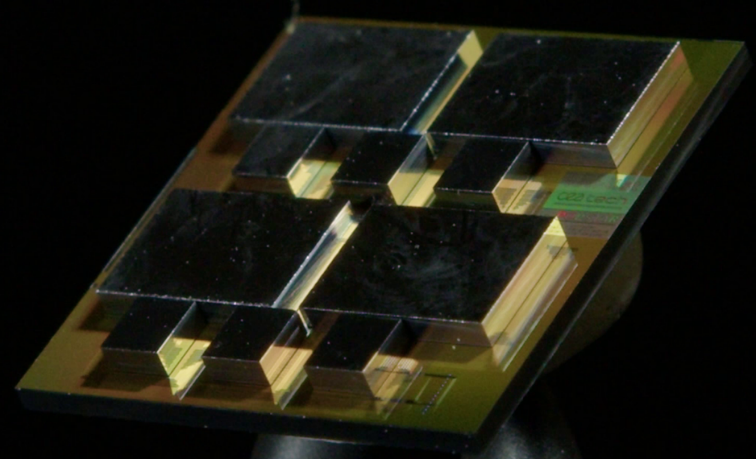

The prototype, described in the ISSCC paper “A 3.19pJ/b Electro-Optical Router with 18ns Setup Frame-Level Routing and 1-to-6 Wavelength-Flexible Link Capacity for Photonic Interposers”, combines photonic switching with integrated CMOS control logic and interface circuitry. The team reports 18 ns optical path setup at the frame level, an energy figure of 3.19 pJ/bit, and an active area of 0.007 mm² per link. The router is implemented in a 28 nm CMOS process and integrated on a photonic interposer.

The technical claim is straightforward: treat optical connectivity across centimetre-scale interposers less like a fixed wiring harness and more like a low-latency fabric whose paths can be established and torn down on demand. To do that, the router dynamically allocates between one and six wavelengths per link, effectively tuning link capacity to workload needs rather than provisioning everything for peak bandwidth all the time.

That matters because electrical fabrics inside large packages pay increasingly painful penalties as distances stretch. Retimers, equalisation, and power budgets scale badly when you are trying to move data laterally across an interposer between compute tiles, cache, accelerators, and high-bandwidth memory. Photonics offers reach and bandwidth density, but historically has struggled to deliver the same kind of fast, fine-grained connectivity control designers expect from packet-friendly electrical networks.

CEA’s approach integrates optical switching, routing control, SerDes, and clocking logic directly with silicon photonics, aiming to remove the gap between photonic devices and system-level protocol control. The prototype is positioned as a proof of concept built on a small-scale multi-die system derived from CEA-Leti’s earlier interposer work, with an architectural target that includes CPUs, GPUs, and HBM in large 2.5D and 3D packages.

Yvain Thonnart, lead author and CEA-List researcher, said, “As chiplet systems continue to grow in scale and complexity, the ability to move data efficiently across the entire package becomes essential. Our goal was to demonstrate that photonic links can provide that reach without sacrificing the flexibility designers expect from modern interconnects. This router is a step toward practical, dynamically routed optical networks that fit within standard CMOS design flows and real product constraints.”

The near-term question is integration economics: how quickly photonic interposer approaches can align with mainstream packaging flows, test strategies, and supply chains, while still delivering a meaningful advantage over ever-improving electrical links. The longer-term direction is clearer — if optical fabrics can be managed at nanosecond timescales, package architects gain more freedom in where they place memory and compute, without paying the same distance tax.