IN Brief:

- EnSilica joins the CHERI Alliance and targets CHERI-enabled ASIC engagements.

- CHERI aims to prevent memory corruption and unauthorised code execution in hardware.

- The Alliance groups industrial members and research bodies to drive deployment.

UK mixed-signal ASIC supplier EnSilica has joined the CHERI Alliance, aligning its custom silicon roadmap with a hardware security approach designed to tackle memory safety failures at the architectural level.

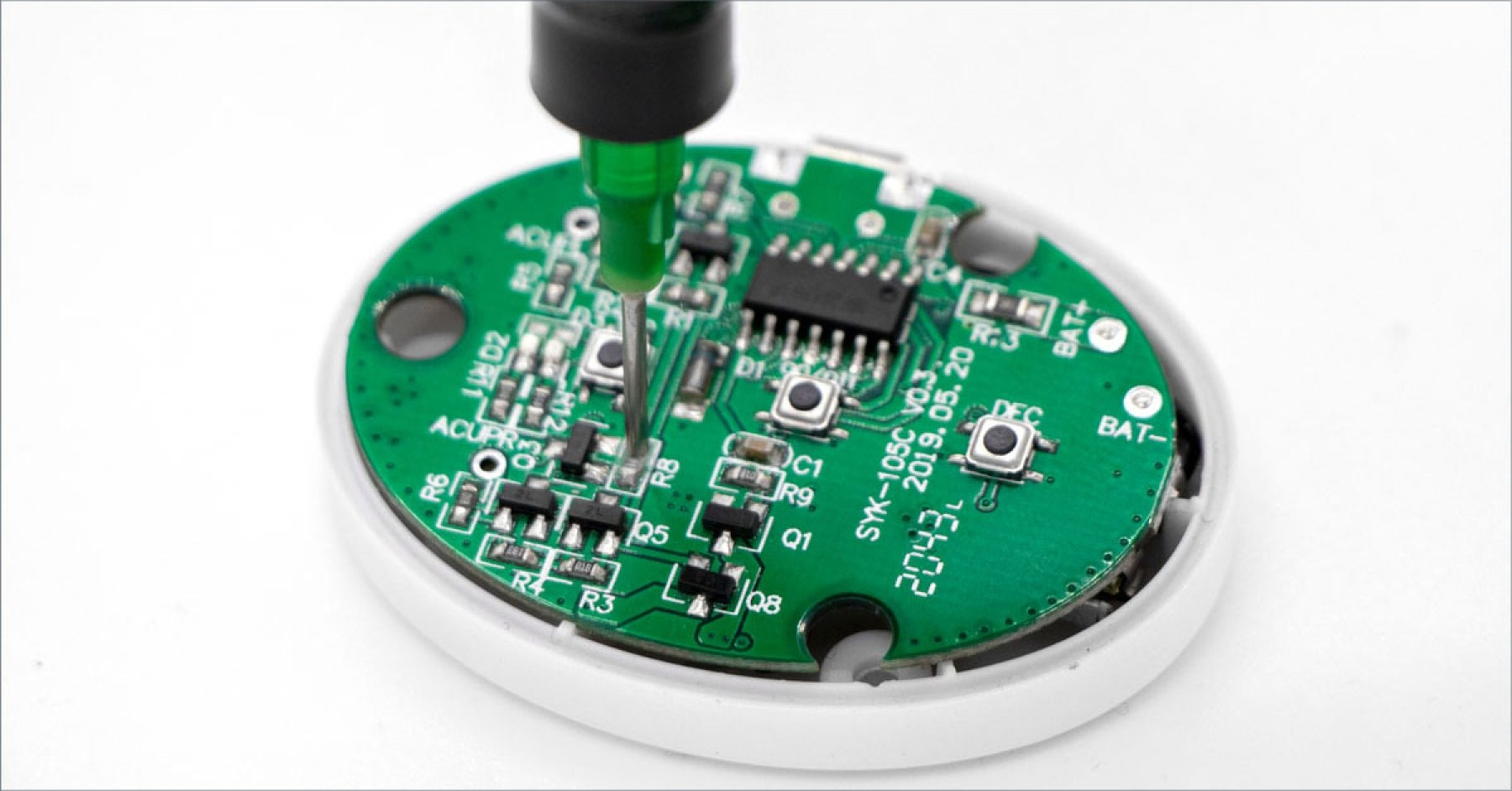

CHERI — Capability Hardware Enhanced RISC Instructions — is positioned by the Alliance as an open technology that strengthens system security by preventing memory corruption and unauthorised code execution, two root causes behind a significant share of exploitable software vulnerabilities. Rather than treating memory safety as a purely software problem, CHERI introduces hardware-enforced memory protection and compartmentalisation, aiming to constrain what code can access, where it can write, and how it can execute, without requiring a full application rewrite.

The CHERI Alliance argues that this approach can be deployed while maintaining performance and power characteristics suitable for embedded systems, a practical constraint for automotive controllers, industrial gateways, and battery-powered endpoints. For ASIC designers, the attraction is straightforward: if a platform can reduce the blast radius of inevitable software defects, it reduces both product risk and the long tail of security maintenance.

EnSilica said it intends to leverage its mixed-signal ASIC capabilities to produce CHERI-enabled designs for customers building “secure by design” systems. The company’s markets span communications, industrial, automotive, and healthcare electronics, where connectivity is now routine and threat models have broadened beyond simple perimeter assumptions.

Ian Lankshear, Chief Executive Officer of EnSilica, said: “Security is a cornerstone of modern computing, and CHERI represents a paradigm shift in how we achieve it. Joining the Alliance allows us to collaborate with the brightest minds in the industry and deliver CHERI’s benefits to our customers at scale.”

For the CHERI Alliance, member expansion is as much about ecosystem completeness as it is about advocacy. The organisation frames itself as a bridge between research and commercial deployment, bringing together industrial members, academic groups, and government organisations to mature tools, software support, and integration patterns. In practice, that means turning a set of architectural ideas into something product teams can validate, certify, and ship, with development environments and OS support that do not collapse under real-world constraints.

The timing is also relevant. Regulators are moving toward tighter product security requirements, and embedded vendors are being asked to demonstrate security properties earlier in the lifecycle, not retrospectively after incident response. Hardware-level memory safety is not a compliance shortcut, but it is one of the few levers that shifts the security baseline without relying on perfect software.

EnSilica’s next challenge will be execution: mapping CHERI approaches onto customer requirements, toolchains, and verification flows, while keeping cost, performance, and time-to-market within the bounds of industrial electronics procurement.