IN Brief:

- Rambus has released HBM4E controller IP aimed at AI accelerators, GPUs, and HPC processors.

- The controller supports up to 16 Gbps per pin and 4.1 TB/s per memory device.

- Rambus is positioning the block for 2.5D and 3D packages, including AI SoCs and custom base-die designs.

Rambus has introduced HBM4E controller IP, extending its high-bandwidth memory portfolio for AI accelerators, graphics processors, and high-performance computing devices.

The company said the controller supports operation at up to 16 Gbps per pin, delivering 4.1 TB/s of throughput to each memory device. In an eight-stack configuration, that scales to more than 32 TB/s of aggregate memory bandwidth, a level Rambus is targeting at next-generation accelerator architectures where memory movement remains one of the key constraints on performance.

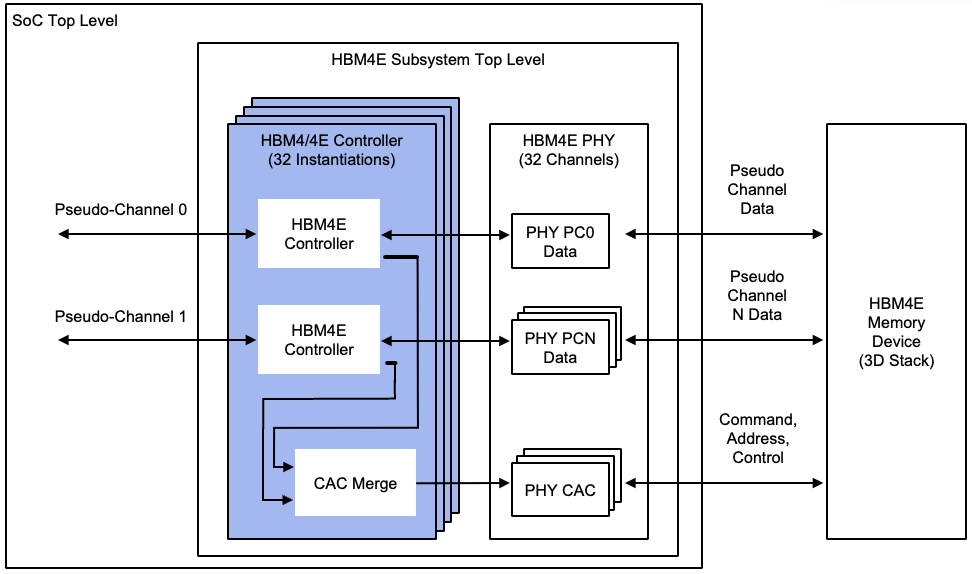

The new IP is designed for integration into complete HBM4E subsystems and can be paired with third-party standard or TSV PHY implementations in 2.5D and 3D packages. Rambus is also pitching the block for use in AI SoCs and custom base-die designs, giving silicon teams a route to assemble broader memory subsystems around licensed controller technology rather than building every block internally.

HBM has become a defining part of the AI silicon roadmap, and controller availability is now just as important as raw memory-device progress. By bringing HBM4E controller IP to market early, Rambus is aiming to secure design wins in the part of the stack where bandwidth, package complexity, and time-to-market increasingly converge.