IN Brief:

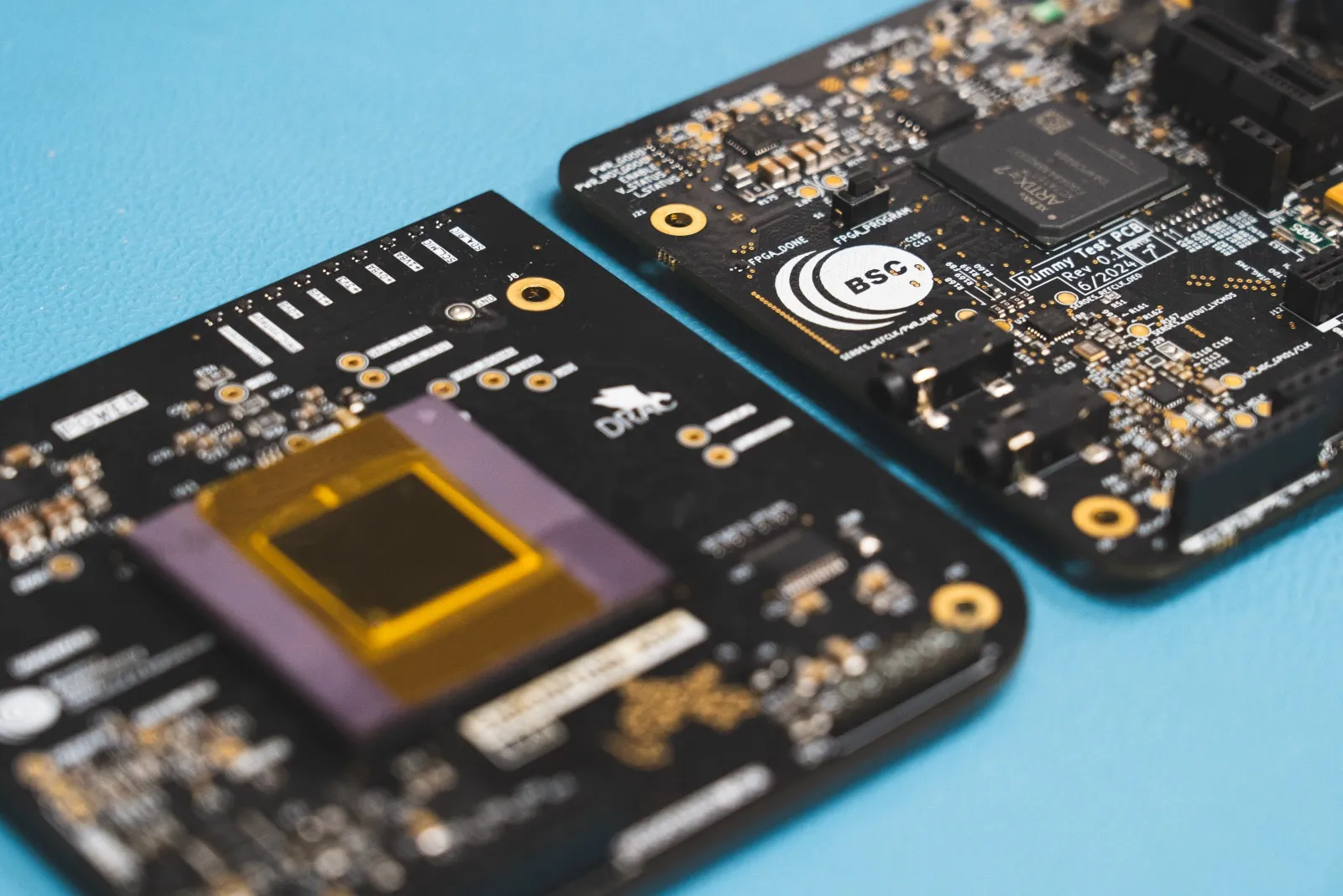

- Safe and Secure Technologies has been launched by BSC and UPC to develop processor-level safety and security technology for critical infrastructure.

- The company’s core Safety Island approach is aimed at monitoring and reliability functions around processors used in power, transport, telecoms, and emergency systems.

- European interest in open architectures, trusted supply chains, and long-life infrastructure platforms is pushing chip design closer to sovereignty and assurance concerns.

Safe and Secure Technologies has been launched in Barcelona as a new semiconductor spin-off focused on processor-level safety and security for critical infrastructure. Created by the Barcelona Supercomputing Center and the Universitat Politècnica de Catalunya, the company is targeting applications where system failure has consequences far beyond product inconvenience, including power networks, transport systems, telecoms infrastructure, automotive platforms, and civil protection systems.

The company’s central technology is a so-called Safety Island, a hardware block intended to sit alongside a host processor and monitor whether the system is behaving within defined parameters. The idea is to provide a dedicated layer for reliability and control functions in systems that are becoming more autonomous, more software-heavy, and harder to certify with confidence when every function is piled into one increasingly complex compute platform. Rather than trying to replace the main processor architecture outright, the Safety Island model is built to supervise it, detect abnormal behaviour, and move the system into a controlled state if necessary.

That is particularly relevant in infrastructure where operational lifetimes stretch far beyond the normal consumer refresh cycle. A utility controller, railway node, airport management system, or emergency-service platform may remain in service for years, sometimes decades, which means hardware choices are made under very different assumptions from those that shape mainstream computing. Designers need determinism, traceability, maintainability, and long-term trust in the hardware base. Once a processor is deployed across a national or regional network, swapping it out is neither cheap nor quick.

Safe and Secure says its technology is aligned primarily with RISC-V, while keeping the security module itself architecturally flexible enough to work more broadly. That matters because the appeal of RISC-V in Europe is no longer limited to cost or academic interest. Open instruction-set control, auditability, and freedom from proprietary licensing dependencies are becoming more strategic concerns as governments and operators look harder at the origin, visibility, and lifecycle implications of the silicon used in critical systems.

The launch therefore lands in the middle of a larger European argument about technological sovereignty. Semiconductor policy in Europe has often focused on manufacturing capacity, investment, and supply-chain resilience, but infrastructure operators are equally concerned with what is actually being designed into their systems. In that context, an auditable architecture has obvious appeal. It does not remove every risk, and it does not solve the foundry question on its own, but it does address a part of the stack that has often been treated as opaque by default.

There is also an engineering shift underway beneath the policy language. Safety and cybersecurity are no longer separate annexes to the design process for connected infrastructure. They are increasingly part of the core silicon and platform discussion, especially where systems must maintain safe behaviour even when faults, anomalies, or malicious interference occur. That is pushing more value into companion functions, supervisory logic, secure boot paths, and hardware mechanisms that can support future cryptographic and regulatory requirements without forcing a complete redesign every time standards tighten.

The company is starting with a fabless model and is still in its early commercial phase, but the proposition is not hard to understand. Infrastructure operators want higher performance and more intelligent automation, yet they are wary of importing complexity that cannot be properly examined or controlled. A monitoring-oriented architecture built for long-life, safety-critical deployments addresses that tension directly. It gives designers a way to pursue more capable systems without pretending that performance alone is enough.

Whether Safe and Secure can turn that research base into volume design wins remains to be seen, but the direction is significant. As compute becomes more deeply embedded in public infrastructure, the industry is likely to place greater value on chips that are not only powerful and efficient, but explainable, auditable, and capable of failing safely. That is a tougher design brief than conventional high-performance silicon, though it may prove more commercially durable in the systems that society cannot afford to get wrong.