IN Brief:

- The VP892 is a SOSA-aligned 3U VPX FPGA processing engine based on AMD’s Virtex UltraScale+ VU13P.

- Abaco says the card delivers 45% more programmable logic and up to 80% more signal-processing engines than the VP891.

- FMC+, 100Gb Ethernet, and dual 100Gb optical interfaces target radar, EW, communications, sensor fusion, and other high-bandwidth workloads.

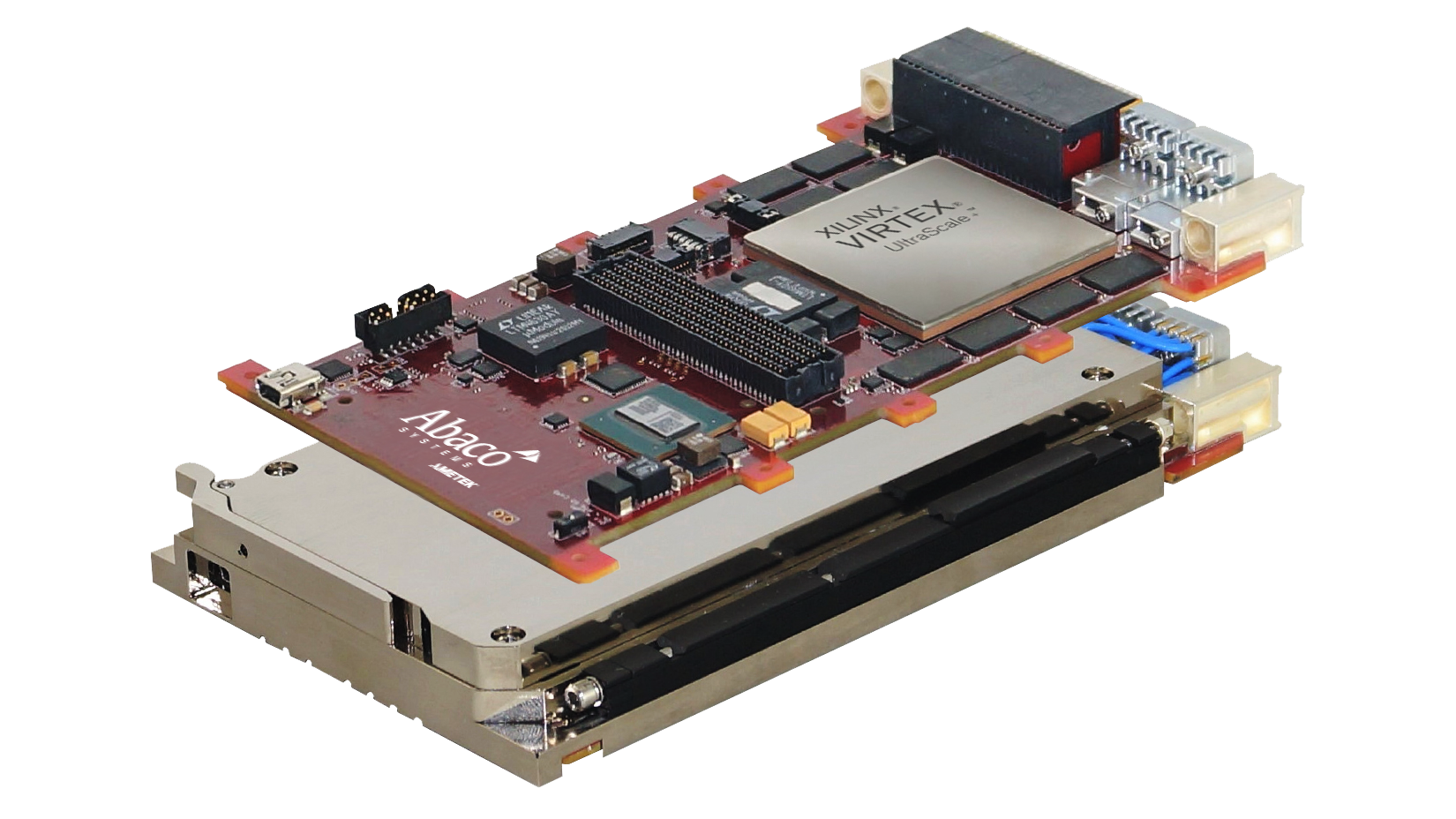

Abaco Systems has introduced the VP892, a rugged 3U VPX FPGA processing engine designed to increase real-time compute capacity in defence, communications, and industrial embedded systems without forcing a break from established open-architecture design practice.

The board is aligned with the SOSA Technical Standard and built around AMD’s Virtex UltraScale+ VU13P, one of the highest-density devices in that FPGA family. Abaco says the VP892 delivers 45% more programmable logic and up to 80% more signal-processing engines than the earlier VP891, creating additional headroom for workloads that now strain older cards through a mix of bandwidth pressure, algorithmic complexity, and tighter latency requirements.

The immediate application list is familiar but important: electronic warfare, radar imaging, communications, networking, and sensor fusion for ISR and autonomous platforms. Those domains continue to push embedded hardware in the same direction, with more channels to ingest, more data to move between cards, and more signal conditioning and inference happening closer to the edge. In radar and EW, that means handling denser waveforms and faster response loops. In communications and networked platforms, it means supporting high-capacity DSP chains and secure data movement. In industrial systems, the same architecture has relevance in inspection, metrology, and other machine-intensive sensing environments where throughput increasingly dictates system value.

Abaco has therefore placed as much emphasis on data movement as on raw FPGA density. The VP892 includes an FMC+ expansion connector for wideband RF and waveform processing, alongside 100Gb Ethernet and dual 100Gb optical interfaces for moving data between cards. That combination points directly at modern systems in which the processing problem is no longer confined to a single board. Sensing, capture, pre-processing, transport, and system-level fusion now have to be treated as one throughput chain, particularly in compact VPX environments where thermal margin and slot count remain constrained.

The longer-term commercial argument behind the product is continuity. Abaco says AMD’s support commitment for the UltraScale+ family through 2045 allows system designers to retain trusted design blocks and verified FPGA work across future upgrades. That matters because the cost of rugged embedded compute is rarely concentrated in the hardware alone. Verification effort, certification evidence, middleware alignment, and backplane-level integration often lock programmes into older devices long after a silicon refresh is technically possible. A new card that raises performance while preserving a familiar architecture can therefore be more valuable than a more disruptive platform leap.

The VP892 also lands into a market that continues to favour modular open systems over tightly closed embedded stacks. SOSA alignment is now part of the commercial requirement set for a large share of new defence processing designs, and the same preference for reusable, standards-based hardware is bleeding into adjacent industrial and communications applications. In that context, VP892 looks less like a single product refresh and more like a signal that higher-end FPGA compute, high-speed optical movement, and programme-life preservation are converging into the same board-level buying decision.