IN Brief:

- Europe’s €830 million FAMES pilot line is moving from infrastructure build-out into practical wafer-sharing work on advanced embedded non-volatile memory.

- CEA-Leti and Fraunhofer IPMS exchanged HZO ferroelectric wafers across 300 mm CMOS fabs and validated contamination control, test vehicles, and electrical characterisation flows.

- The next phase moves toward array-level evaluation on GlobalFoundries 22nm FDX and broader work across FeRAM, FeFET, MRAM, and OxRAM.

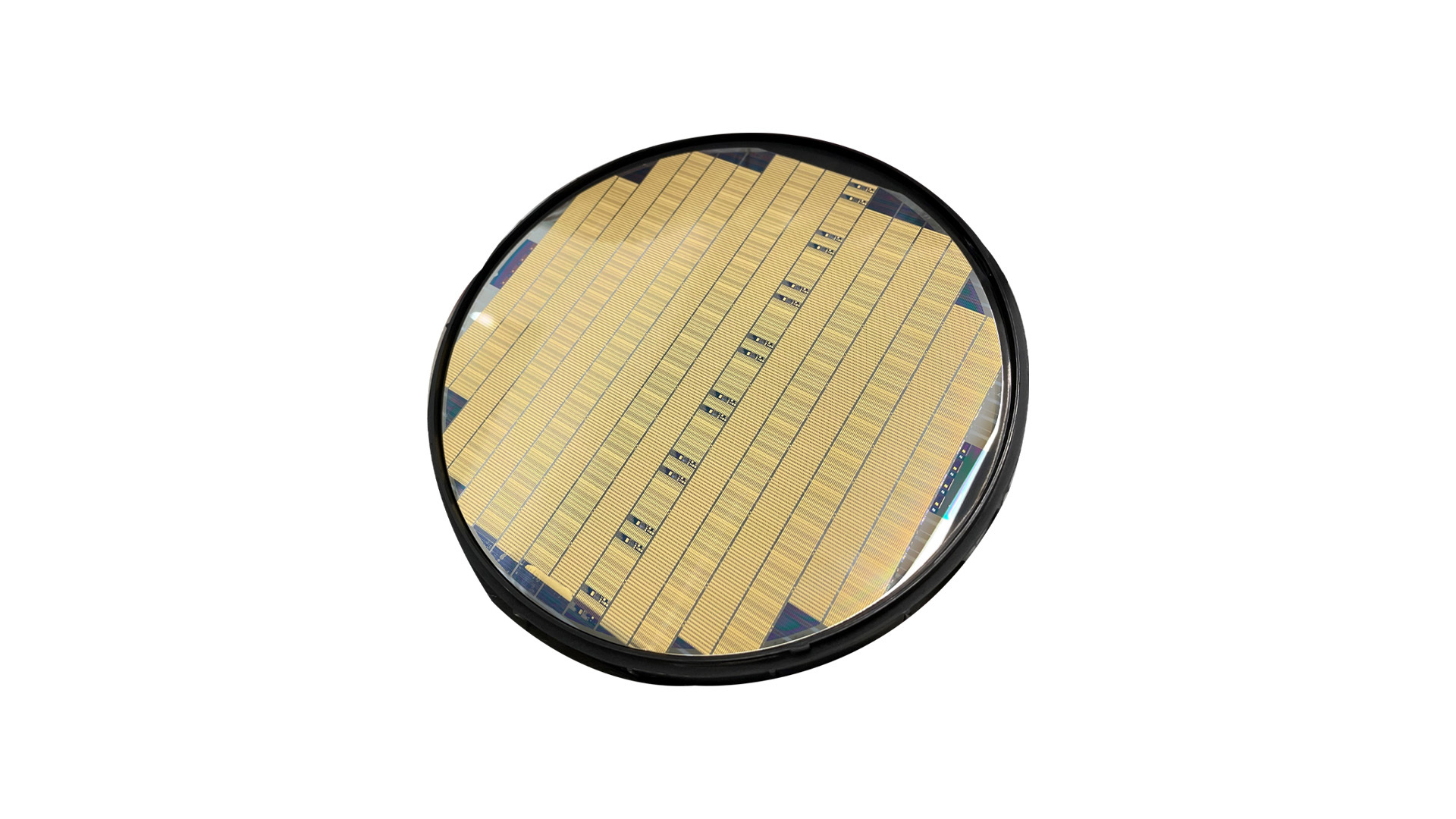

CEA-Leti and Fraunhofer IPMS have completed the first ferroelectric memory wafer exchange within the FAMES pilot line, a step that carries more weight than a routine wafer hand-off. The exchange was built around hafnium-zirconium oxide ferroelectric capacitor stacks and was intended to prove that advanced memory materials can move between leading European 300 mm research fabs without losing process integrity or derailing characterisation.

The work focused on short process loops covering fabrication and electrical evaluation of HZO-based structures. Standardised contamination control sat at the centre of the exercise, with the teams using VPD-ICP-MS and TXRF analysis to confirm that the wafer flow remained within limits as it moved between sites. Devices were then assessed on a ferroelectric capacitor array test vehicle designed by CEA-Leti, using PUND characterisation to separate genuine ferroelectric switching from parasitic effects.

That kind of process discipline is what turns a pilot line from a funding framework into something engineers can build around. Early results also produced a useful materials signal: titanium nitride bottom electrodes outperformed tungsten in the initial screening work, showing lower failure rates after 107 field cycles at 4 MV/cm. Different electrode splits also produced clear behavioural differences, giving the consortium a sharper basis for tuning stack design, reliability work, and future integration choices.

The broader context matters. FAMES was inaugurated in Grenoble on 30 January 2026 as the first operational pilot line under the European Chips Act framework, with €830 million in combined investment and a focus on FD-SOI technologies built for lower-power operation. The ferroelectric wafer loop now feeds directly into the next development stages, which include integrating HfO₂-based ferroelectric stacks into CEA-Leti CMOS flows and pushing array-level evaluations onto GlobalFoundries’ 22nm FDX Memory Advanced Demonstrator multi-project wafer shuttle.

That roadmap also connects to compute-in-memory work already under way at Fraunhofer IPMS following a first 22nm FDX tape-out. In other words, the wafer exchange is not just a process validation milestone; it is part of a much larger effort to turn Europe’s ferroelectric memory research base into a shared development platform with credible paths into embedded FeRAM, FeFET, and related low-power memory architectures. Details of the wider programme are available on the FAMES pilot line website.