IN Brief:

- TPK and ASE plan a through-glass via packaging pilot line in 3Q26 for glass substrates aimed at high-end computing ICs.

- The move pushes TPK beyond touch panels and into advanced packaging, where warpage control, routing density, and signal integrity are central design concerns.

- Glass-core packaging is gathering momentum across AI and HPC, but process maturity, yield, and line integration remain the immediate hurdles.

TPK is moving with ASE into through-glass via packaging, with the partners targeting a pilot line in the third quarter of 2026 for glass substrates aimed at high-end computing ICs. The project marks a notable step for TPK, which has been best known for touch technology and display-adjacent manufacturing, but is now looking to establish a position in one of the semiconductor industry’s most closely watched packaging transitions.

The immediate focus is on glass substrates for advanced devices where package size, signal density, power delivery, and mechanical stability are becoming harder to manage with established materials and architectures alone. A pilot line does not amount to volume manufacturing, but it does move the conversation on from laboratory feasibility to process integration, equipment selection, yield learning, and customer qualification. That is the point at which packaging roadmaps become real engineering programmes rather than future-facing slideware.

Glass has been drawing attention because it promises a different balance of properties from organic build-up substrates and silicon interposers. Flatness, rigidity, and lower warpage have become increasingly valuable as package dimensions grow and as designers pack more I/O, memory bandwidth, and heterogeneous die combinations into a single assembly. Through-glass vias also offer a route to finer routing and better high-frequency behaviour, which is why glass has moved rapidly into discussions around AI accelerators, high-performance computing, co-packaged optics, and other bandwidth-hungry devices.

That does not make the path straightforward. Forming reliable vias in glass, metallising them consistently, handling large panels without damage, and fitting new substrate flows into existing assembly and test environments are all non-trivial manufacturing problems. The attraction of glass lies in the potential system-level gains, but those gains only matter if the process stack can deliver repeatable yield, stable dimensional control, and commercially acceptable cycle times. A 3Q26 pilot line therefore looks less like a finish line than the start of a more demanding phase of engineering validation.

The timing is not accidental. Advanced packaging has moved much closer to the centre of semiconductor competition as AI infrastructure pushes up demand for chiplets, high-bandwidth memory integration, wider interfaces, and larger package footprints. In that environment, substrate technology is no longer a passive enabling layer. It is becoming a constraint, and in some cases a differentiator. Package architects are being asked to solve thermal density, power integrity, interconnect scaling, and manufacturability at the same time, which is exactly why new substrate materials are receiving so much attention.

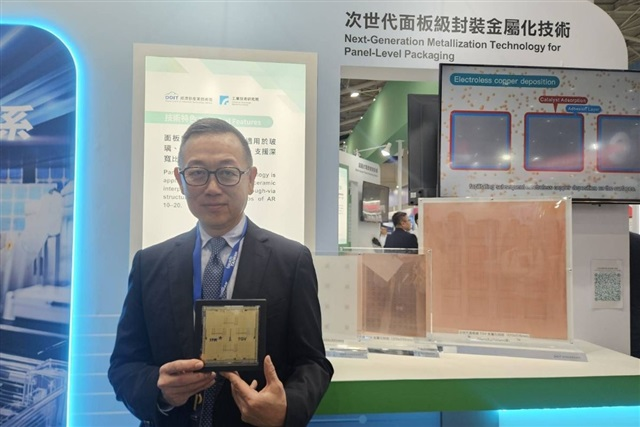

The wider field is also becoming more crowded. Japanese materials and printing groups, glass specialists, and Chinese display-linked manufacturers have all been moving deeper into TGV-related development. That matters because no single company will determine whether glass-core packaging reaches broad adoption. The transition depends on a stack of capabilities — materials, via formation, metallisation, panel handling, inspection, packaging design, and OSAT execution — all maturing together. TPK’s display manufacturing heritage may prove useful here, especially if it can adapt panel-scale process knowledge to the tighter tolerances and qualification expectations of semiconductor packaging.

For ASE, the appeal is equally clear. The largest packaging groups need access to substrate options that can support larger, more complex advanced packages without surrendering yield or economics. If the pilot line lands on schedule and produces stable process data, the TPK-ASE pairing could become an important signal that glass substrates are moving from speculative promise into practical packaging development. The industry has heard plenty about glass. It now needs evidence that it can be manufactured, scaled, and designed around with fewer compromises than the materials it is meant to augment or replace.